修考数字电路内容复习📒

Reference: 黑书,坂井

第一章:进制

十六进制(Hexadecimal),十进制(Decimal),二进制(Binary),进位(carry bit)

微处理器处理的一块数据称为字(word)。字的大小取决于微处理器的结构。

原码反码补码参考计组

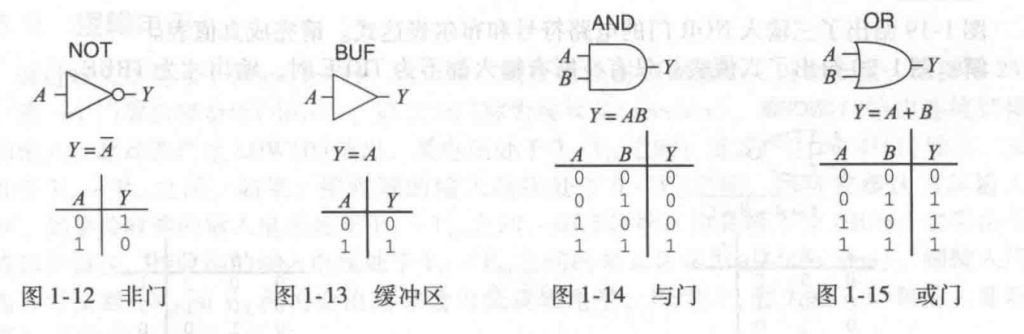

基础逻辑门器件:三角符号表示一个缓冲器(仅仅将输入复制到输出),与门运算与或交(intersection)

或门运算并(union)或(or)

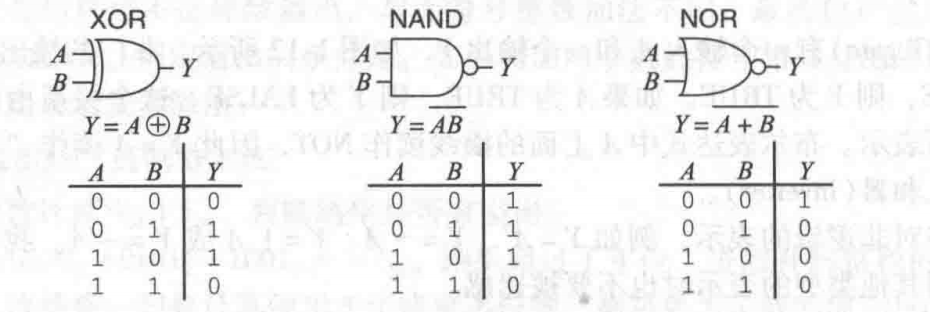

异或(exclusive OR, XOR):相异为1,相同为0。

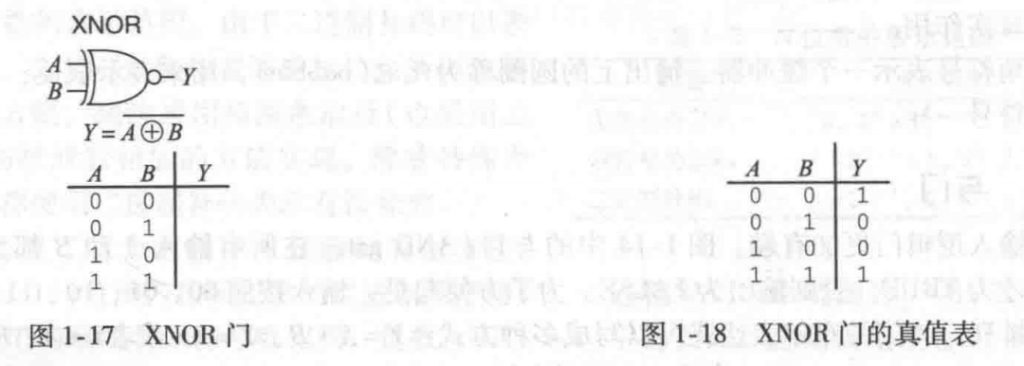

同或,也叫异或非(XNOR):就是在异或门的基础上加一个气泡取反,相同为1,相异为0

第二章:组合逻辑设计

组合逻辑电路(combinational circuit):输出仅仅取决于输入的值,是没有记忆的,电路不包含回路。

布尔表达式(Boolean equation):非(complement)是反,AND称为乘积项(product)或者蕴含项(implicant)。

最小项(minterm): 包含全部输入变量的乘积项。

最大项(maxterm): 包括了全部输入项的和。注:画真值表,找0的式子,最大项是和的乘积都为0 = 0 * 0*0……(真值表里面有1的项则取反)

与或式(sum-of-product):例如S = AB + BC

或与式(product-of-sums): 例如S = (A + B)(B + C)

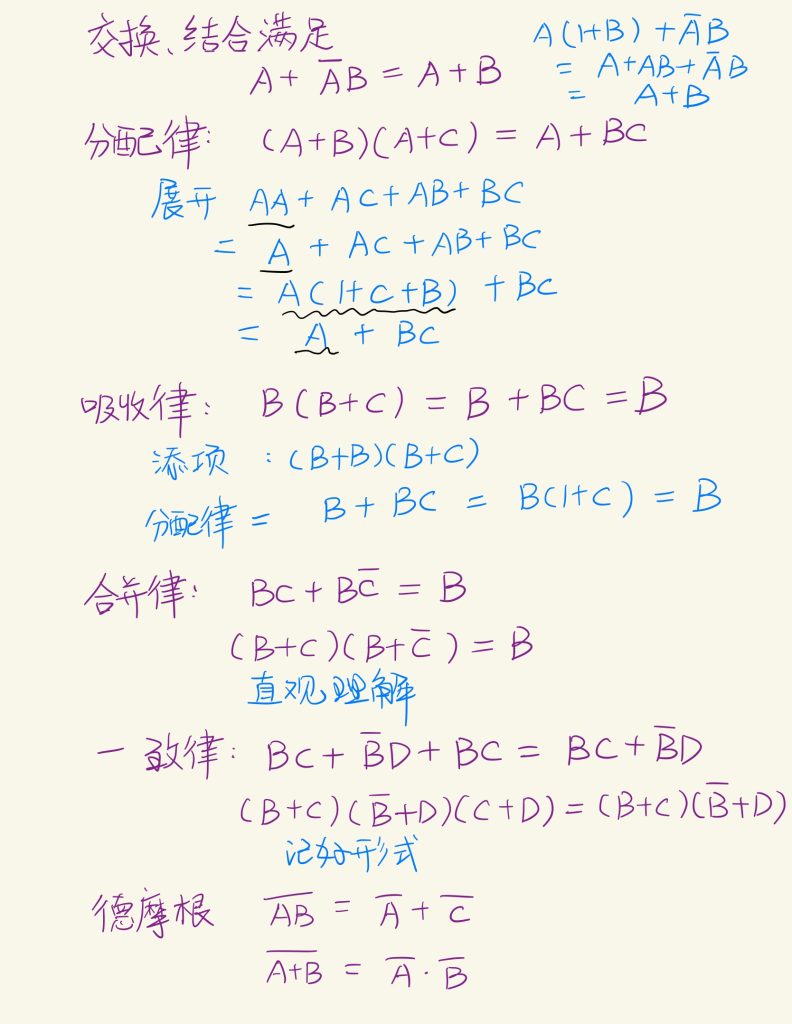

布尔运算定律⬇️

电路原理图(schematic): 写出逻辑表达式然后画电路图就好

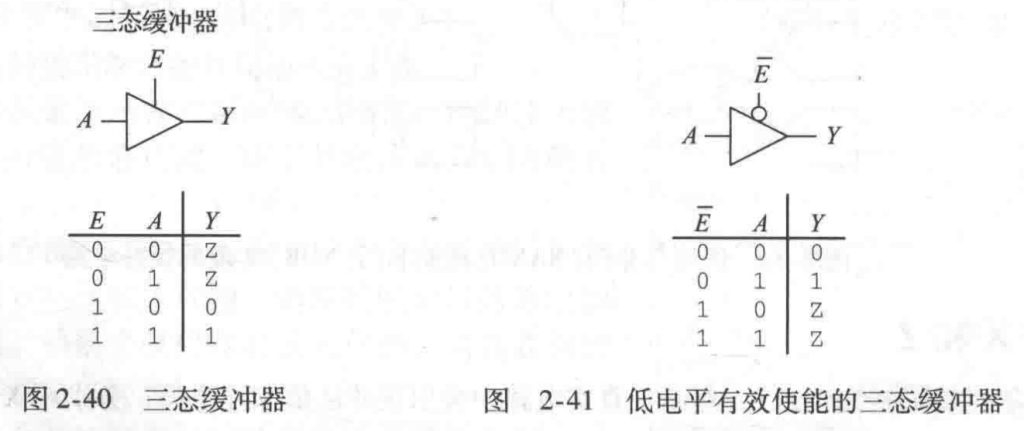

三态缓冲器(trismate buffer):⚠️注意使能端是高水平有效or低水平有效,使能端等于一个放行的作用。注意使能端不放行的时候,Y的输出是Z(称为浮空floating,表示结点没有高电平和低电平驱动)

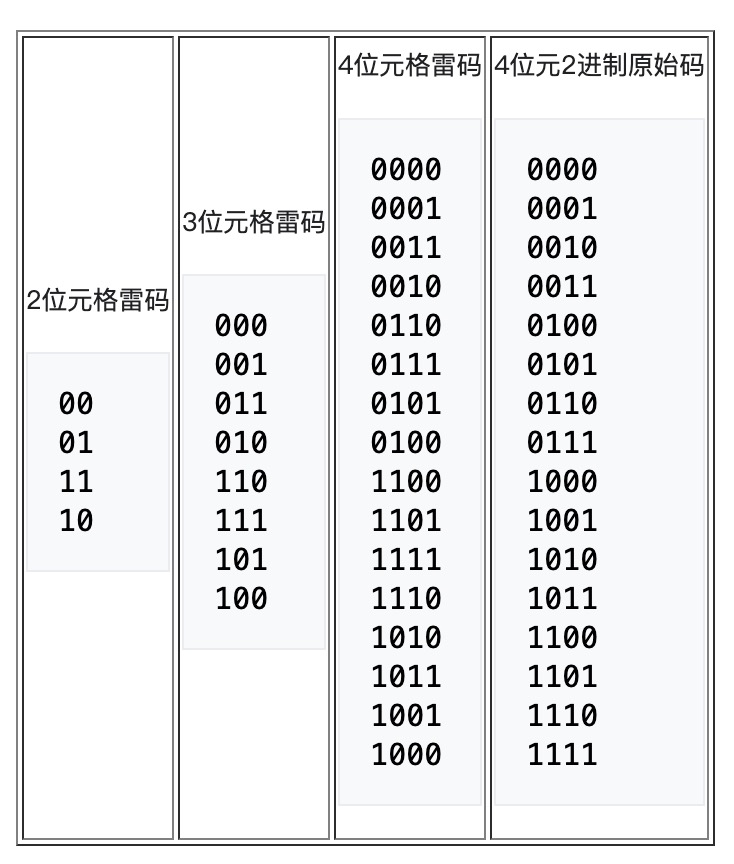

卡诺图(Karnaugh map, K-map):要用格雷码(Gray code)表示。画法一句话概括就是用尽量少且尽量大的圈来圈住卡诺图中所有为1的方格。(边长必须为2的整数次幂;i.e.,1,2,4,8……)

格雷码的发明即是用来将误差之可能性缩减至最小,编码的方式定义为每个邻近数字都只相差一个位元,因此也称为最小差异码,可以使装置做数字步进时只更动最少的位元数以提高稳定性。

无关项(Don't-care term):无关项可以认作0或1,因为对输出没有影响。在卡诺图化简中,可以引入无关项然后圈起来,可以更好地化简逻辑式。

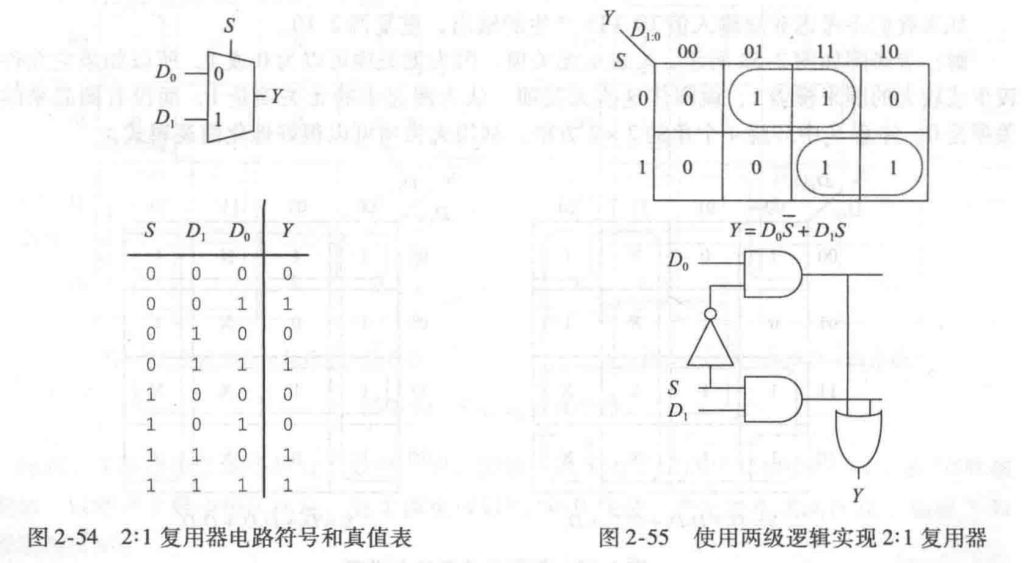

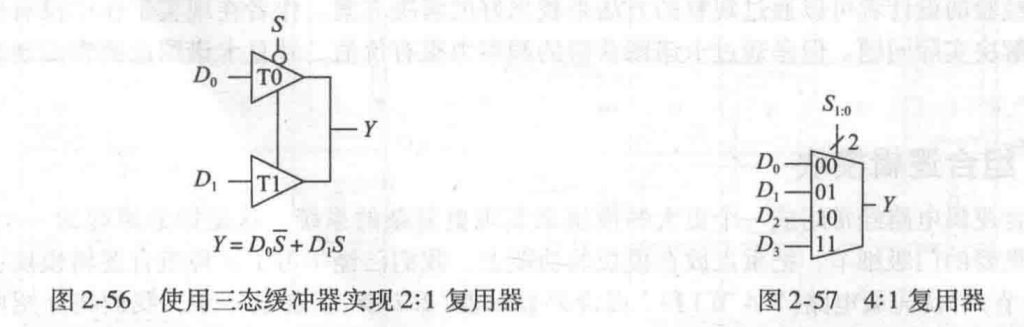

复用器(multiplexer): 2比1复用器是指有两个输入D1、D0和一个选择输入S和一个输出Y。S是控制信号(control signal)相当于起一个单刀双掷开关的作用。复用器可以用三态缓冲器实现。注意4:1复用器的画法,要注明控制信号有几根线……

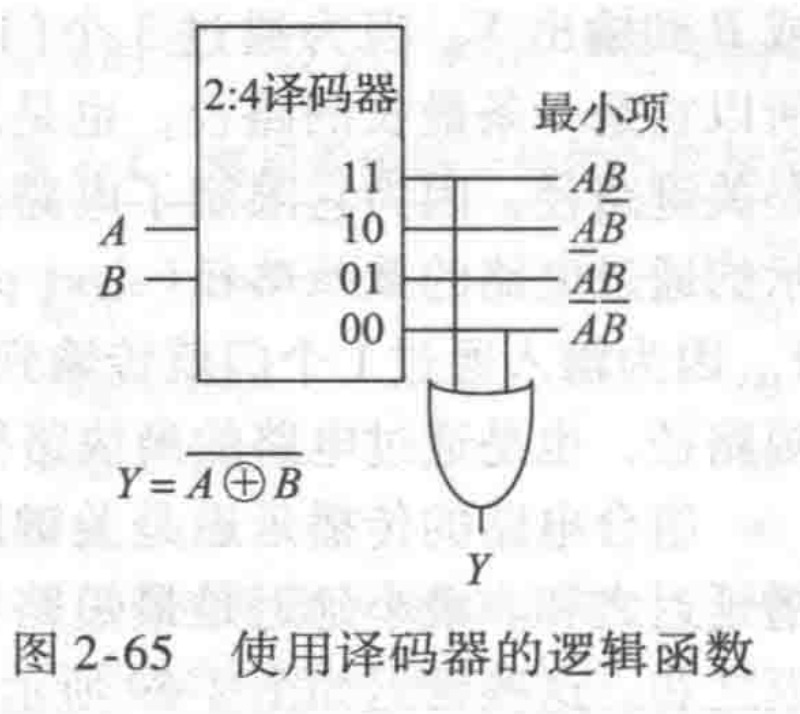

译码器(Binary decoder):N个输入对应2^N个输出,通俗来说就是给一个二进制串找到它的输出口,一个n位二进制串自然潜在对应的输出口有2^N个。译码器的输出称为独热编码(one-hot),每个状态由一个多位的二进制数表示,而在任何给定的时间里,这个二进制数中只有一位是1,其余各位都是0。译码器也可以用来实现逻辑函数!

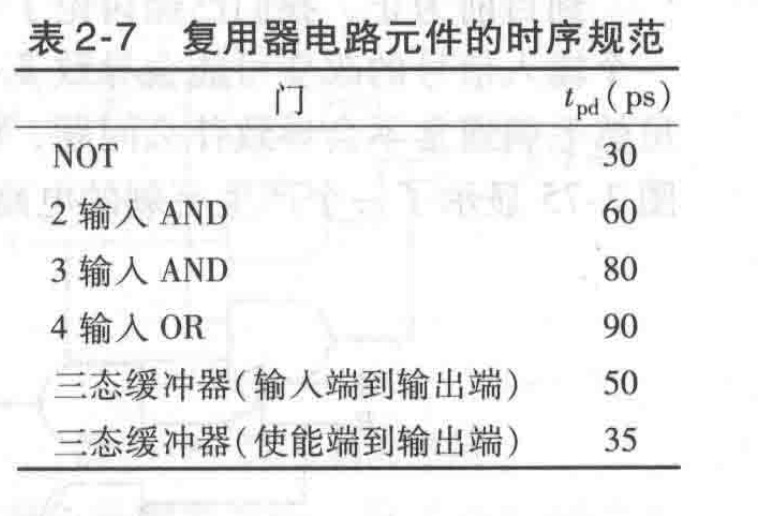

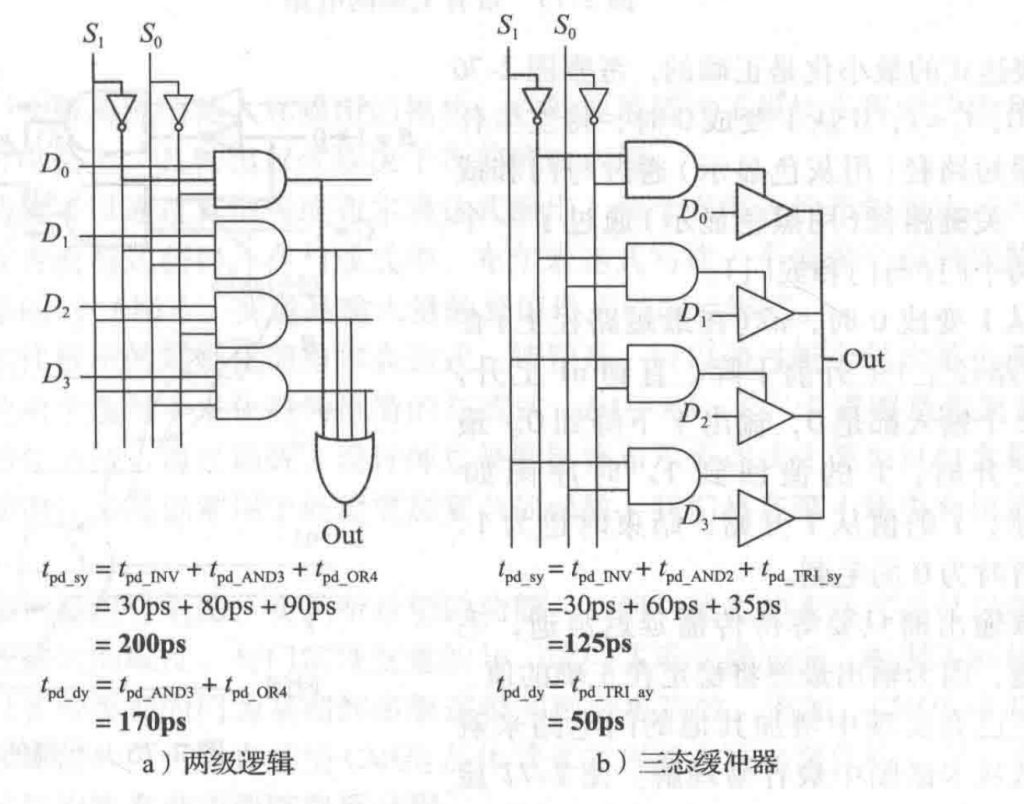

传播延迟(propagation delay):当输入改变直到一个或多个输出达到他们的最终值所经历的最长时间。

最小延迟(contamination delay):当一个输入发生变化直到任何一个输出开始改变的最短时间。

组合电路的传播延迟是关键路径(critical path)上每一个元件的传播延迟之和。

组合电路的最小延迟是最短路径(short path)上每一个元件的最小延迟之和。

可以参考黑书的例子🌰注意路径是从输入开始到输出!

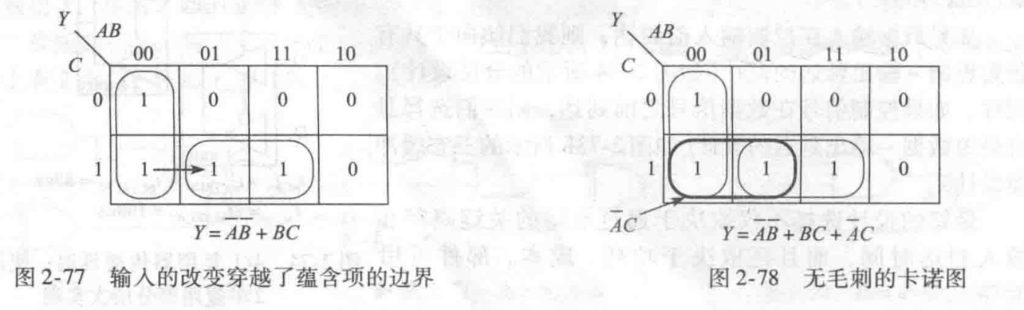

毛刺(glitch)也叫做冒险(hazard),指的是一个输出信号改变导致多个输出信号改变的情况。为了避免毛刺,可以在卡诺图画圈的时候,避免两个圈相切的情况,可以多加一个圈把两个相切的圈给覆盖起来,但也会为额外的硬件成本付出代价(也就是没办法占便宜😭不能既要,还又要)

第五章:数字模块

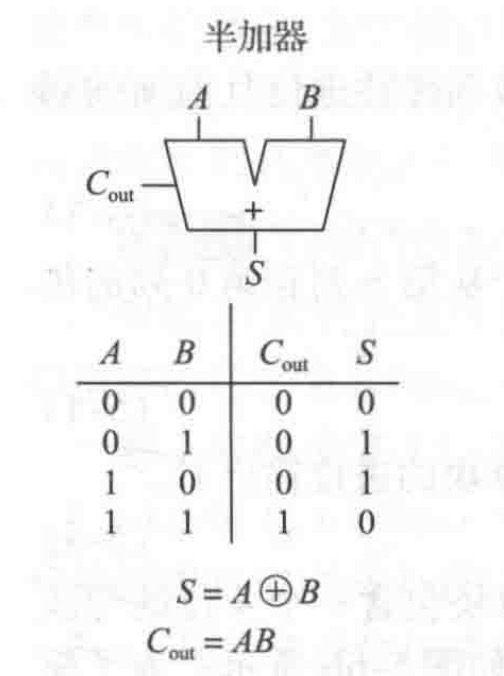

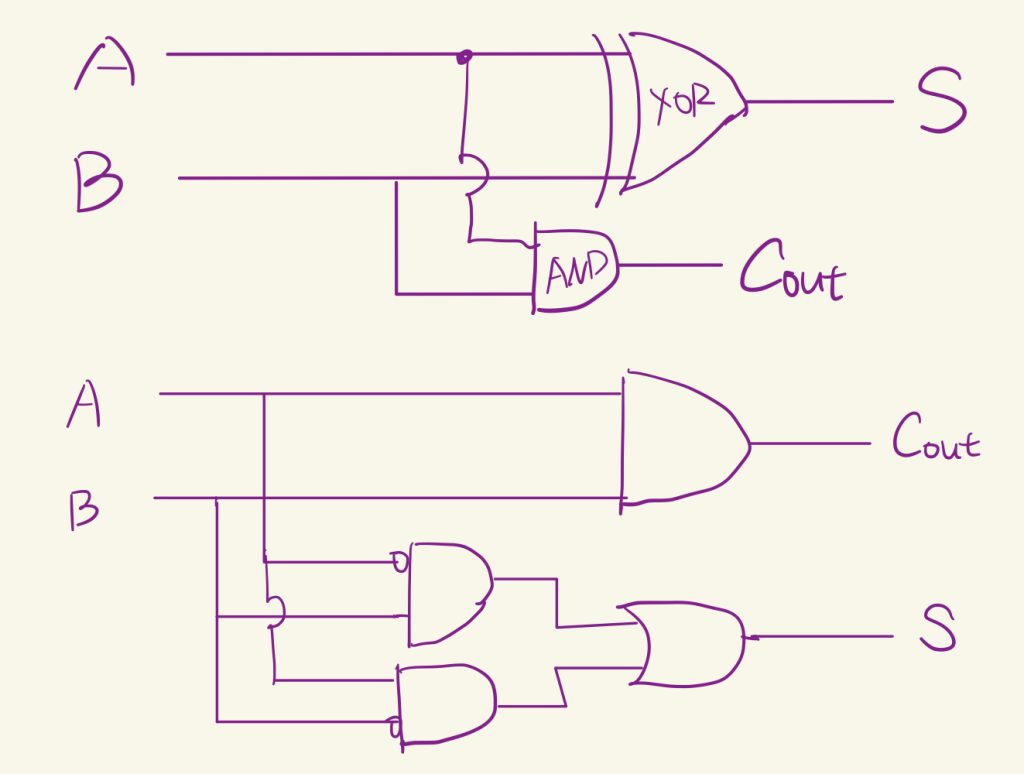

半加器(half adder):通俗来说就是不考虑进位的加法器,只有两个输入和两个输出:输入A和B,输出和数sum和进位cout。A⊕B = A'B + AB'

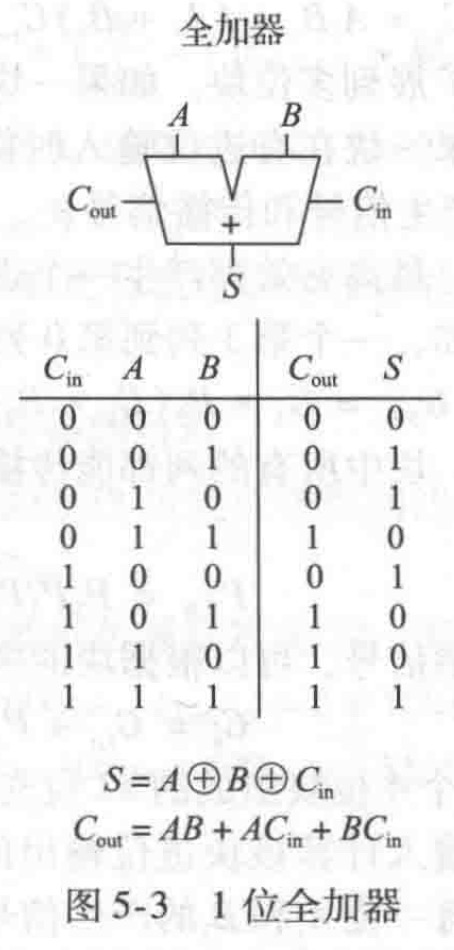

全加器(full adder):全加器就是在半加器的基础上引入一个进位输入,总共三个输入两个输出。

Cout有多种表示方式,如果用2个半加器实现全加器的设计如下。一位全加器应用于个位时,需要将进位输出接到地,即置为0。

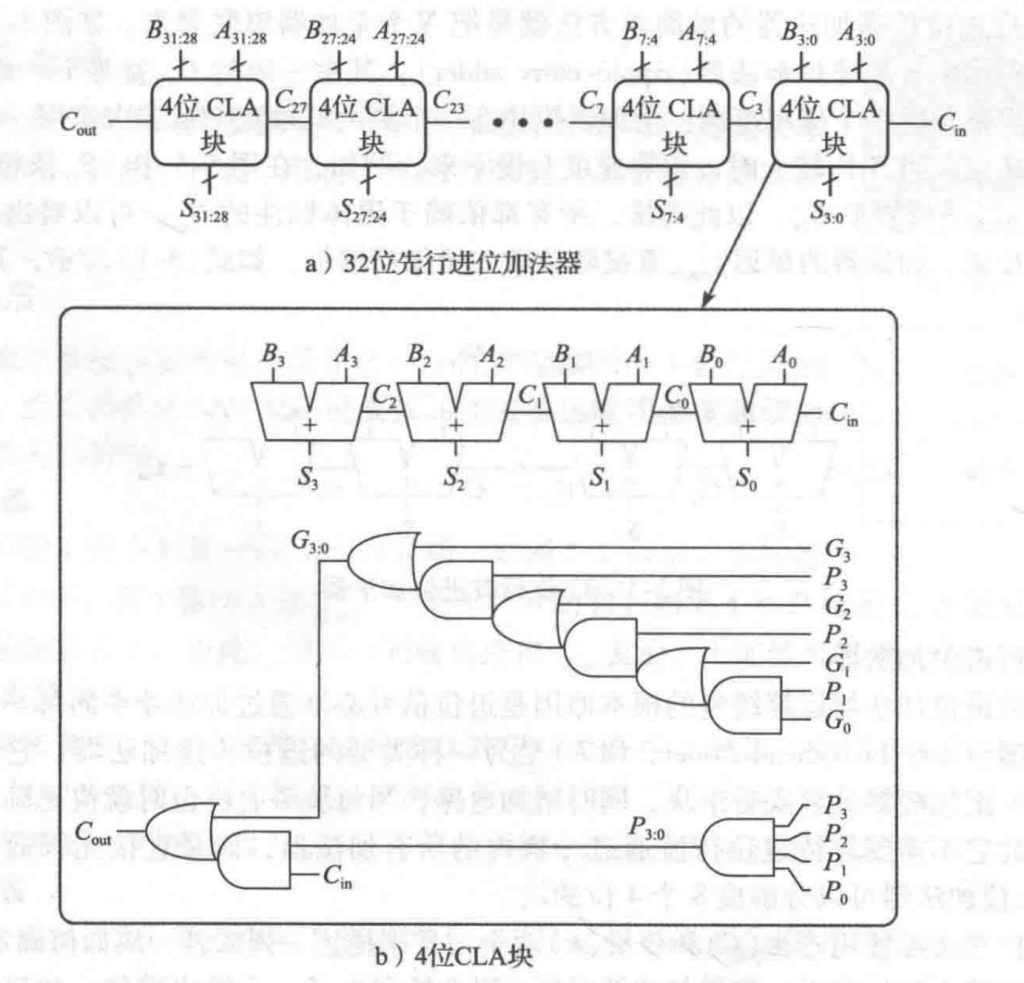

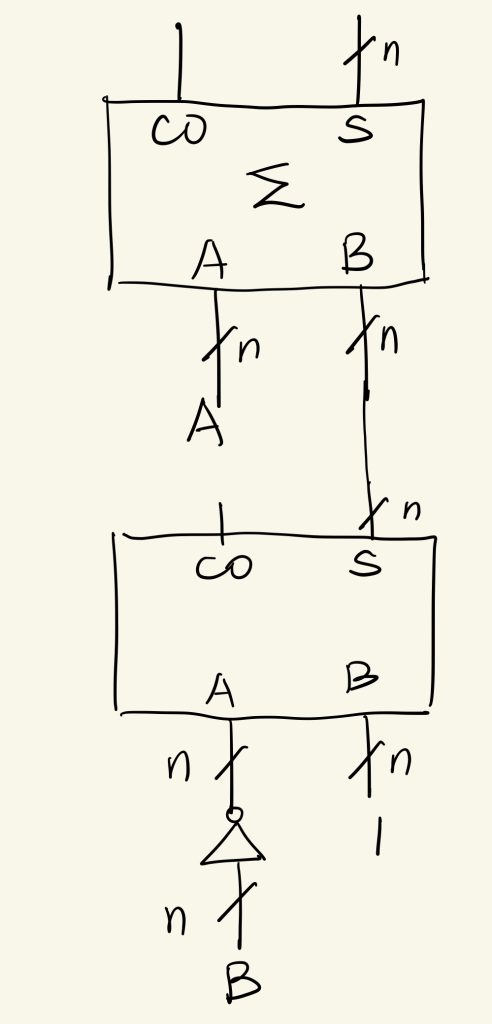

行波进位加法器(ripple-carry adder):最简单的实现方法,把N个全加器串联起来。该加法器的延迟t_ripple随位数的增加而增加。简单来说就是模拟列竖式计算🧮。

先行进位加法器(Carry-Lookahead Adder,CLA):把加法器分成若干块,同时增加电路,当每块一有进位的时候就快速确定此块的输出进位。因此它不需要等待进位行波通过一块内的所有加法器,而是直接先行通过该块。例如一个32位加法器可以分解成8个4位的块。体现了模块化和规整化。类比算法里的分治递归策略来理解。

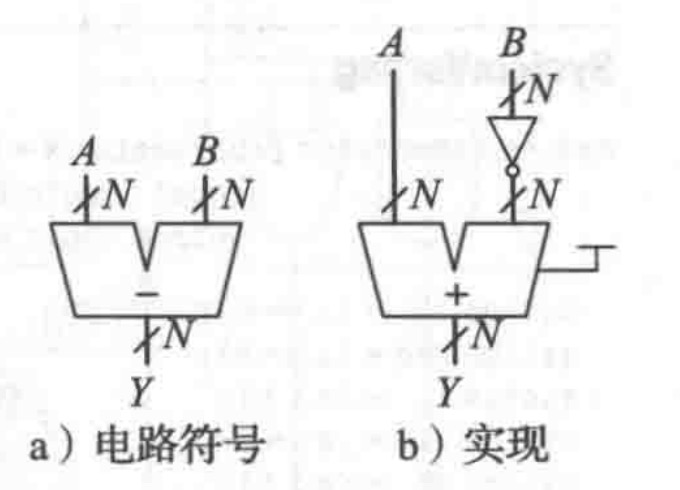

减法器(subtractor):减法器的实现可以用加法器来:因为是用补码进行运算,所以可以对被减数取反➕1,实现的逻辑就是 A - B = A + (B' + 1)。

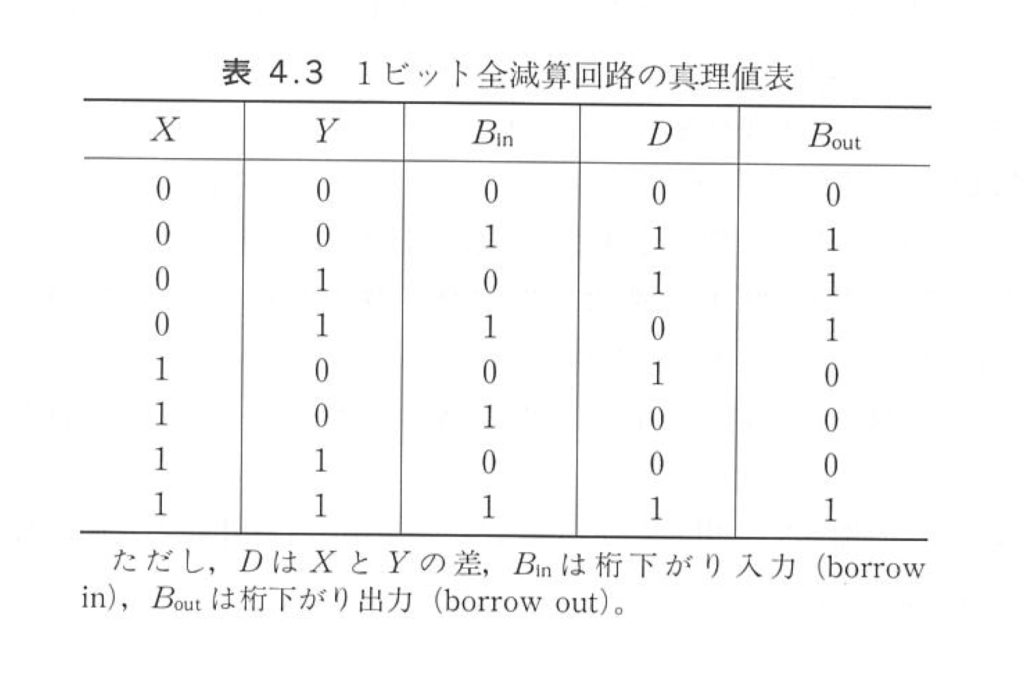

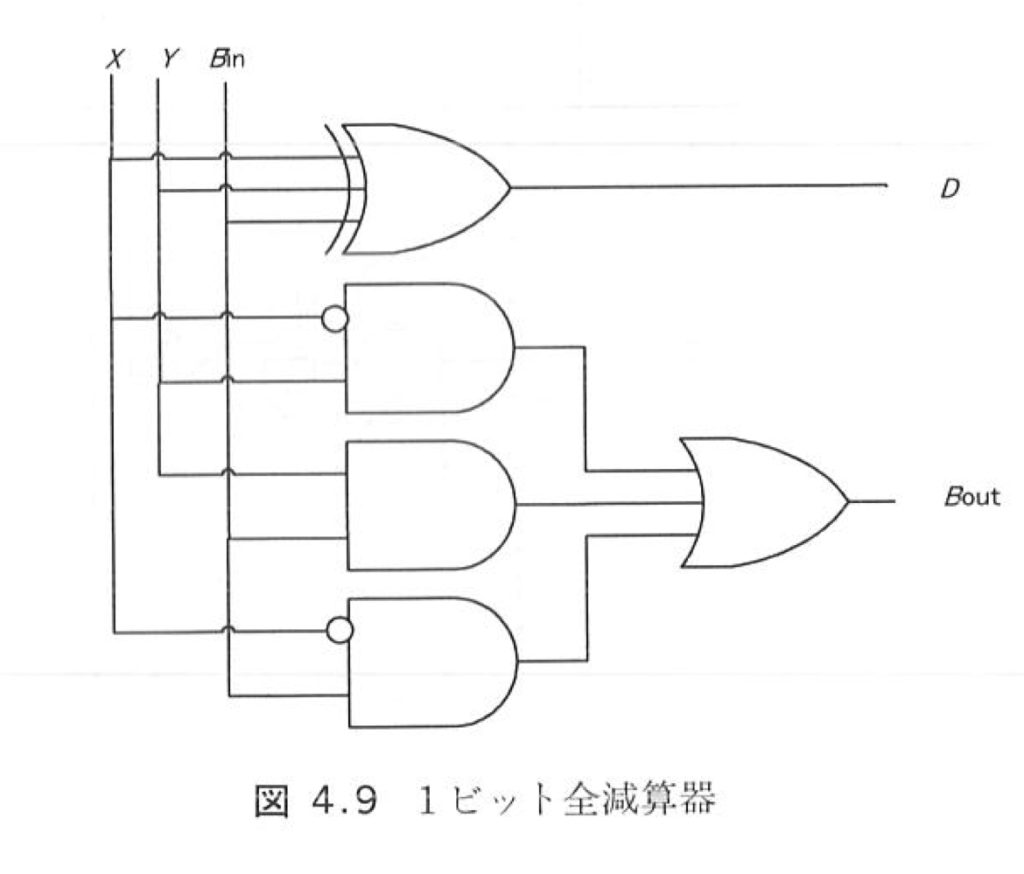

在实现1位减法器的时候,就正常列真值表,卡诺图化简,画电路图

S = X⊕Y⊕Bin,下图Bin表示X有没有被借位,Bout表示X是否需要向前借位

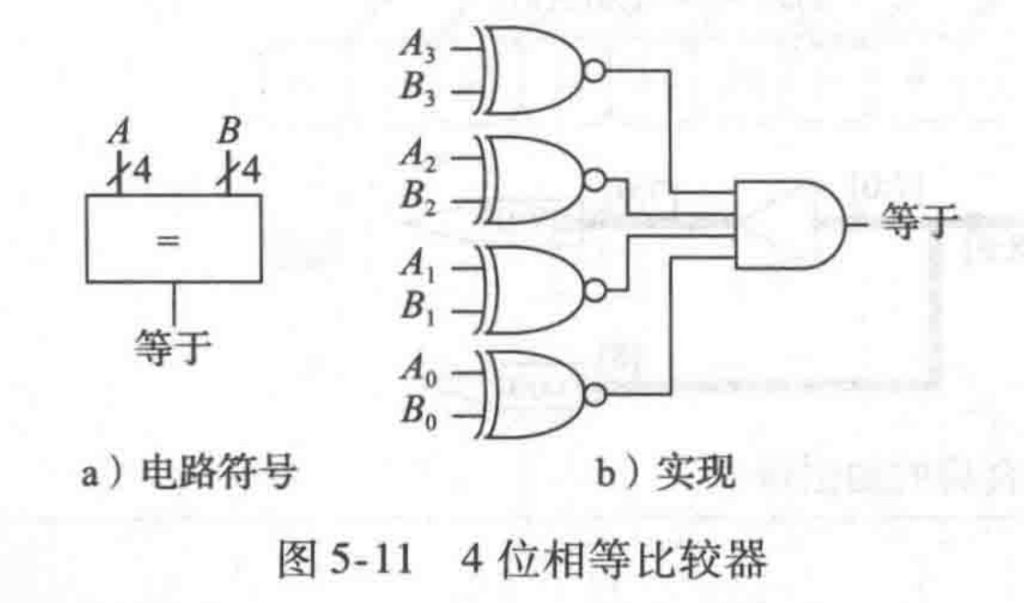

相等比较器(equality comparator):产生一个输出,说明A是否等于B(A==B),实现简单,只需要XNOR检查A和B中的每一位是否相等,如果所有位都相等(AND),则相等。

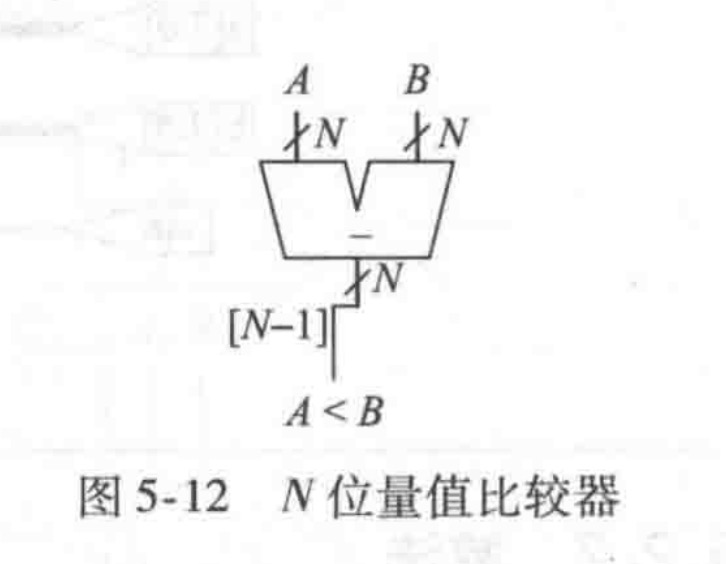

量值比较器(magnitude comparator):首先计算A-B的值,然后检查结果的符号位(最高有效位),如果结果是负的(即符号位为1),则A<B;否则A>=B.

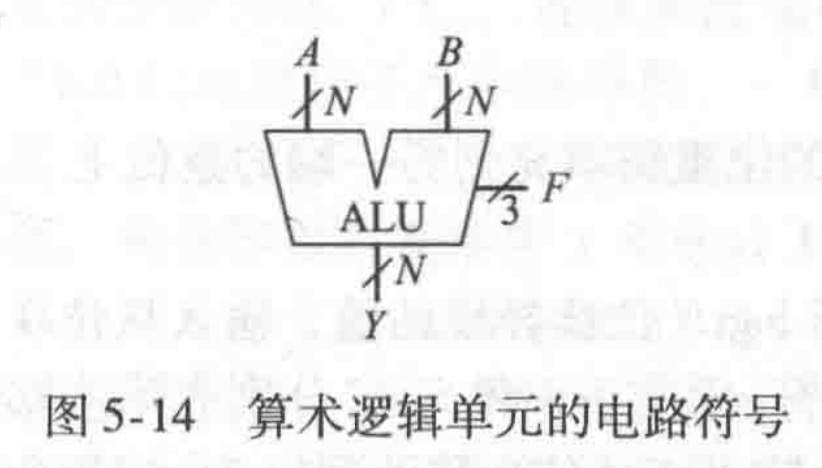

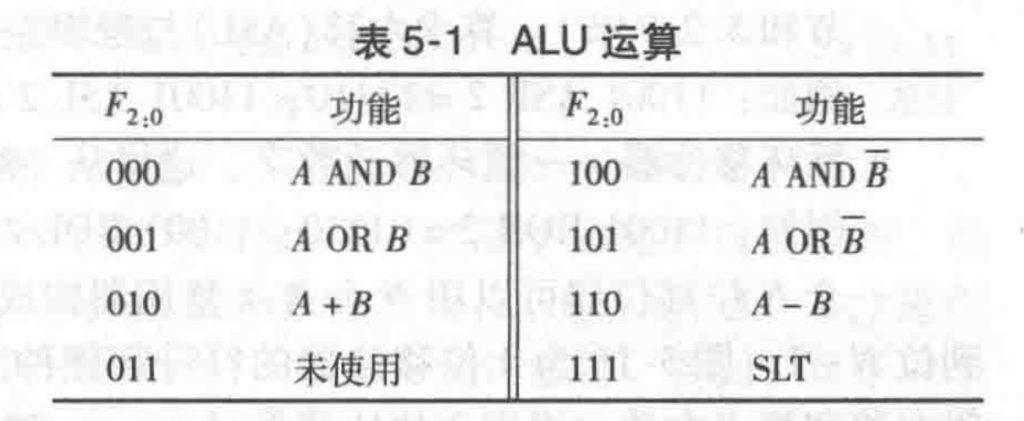

算术逻辑单元(Arithmetic/Logical Unit, ALU)将多种算数运算组合到一个单元内。例如,典型的ALU可以执行加法、减法、量值比较、AND和OR运算。下图给出的是N位输入N位输出的ALU,控制信号F指出ALU可以执行的功能。

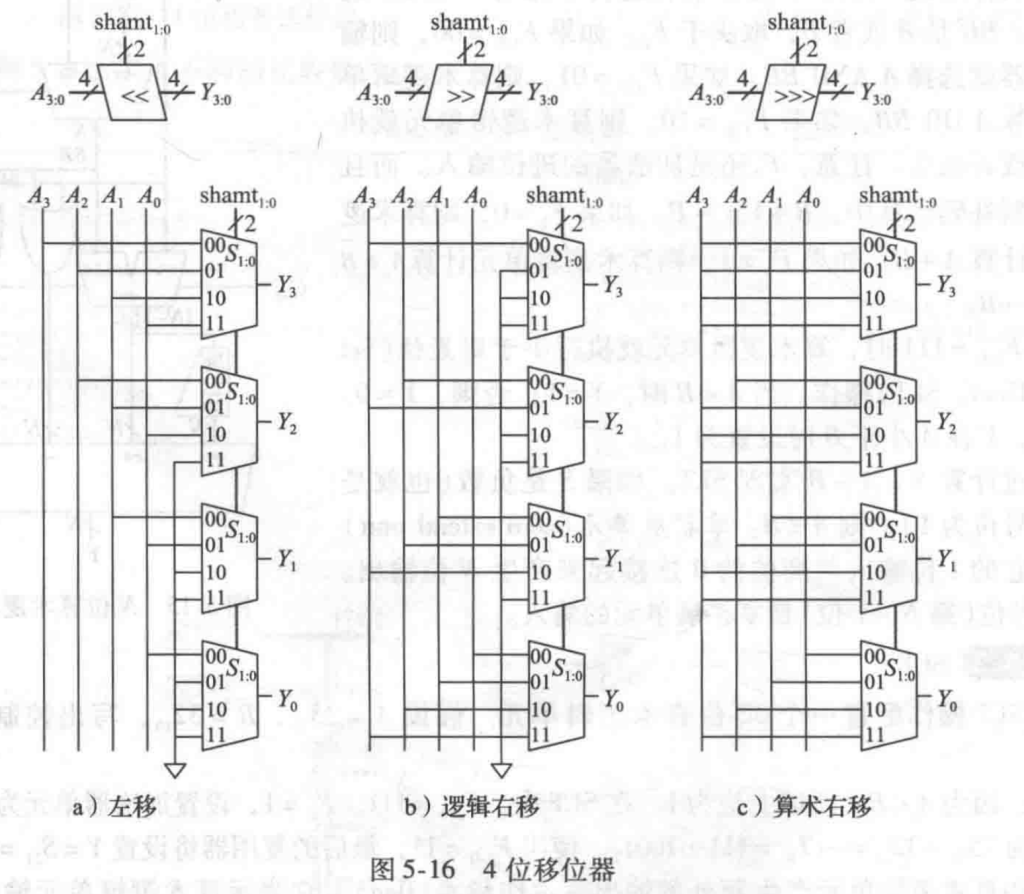

移位器(shifter):用来完成2的幂的乘法或触发。

⚠️注意对于有符号整数的右移操作,右移时会保持符号位不变。如果原始数是负数(即符号位为1),则右移时会在左边补1,以保持负数的符号。如果原始数是正数(即符号位为0),则右移时会在左边补0。

第三章:时序逻辑电路设计

⚠️时序逻辑的电路元件都有记忆的功能!

PS:黑书这一章写的真的烂!阅读困难!而且为什么要在第三章讲时序电路然后在第五章讲算数电路?

维基百科:https://zh.m.wikipedia.org/wiki/%E8%A7%A6%E5%8F%91%E5%99%A8

各器件功能特性:https://blog.csdn.net/qq_43581718/article/details/105838335

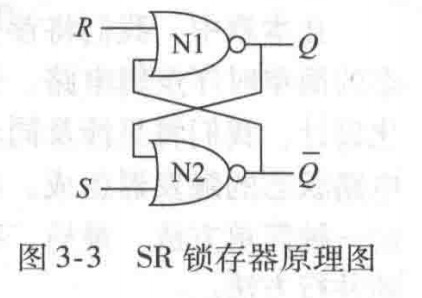

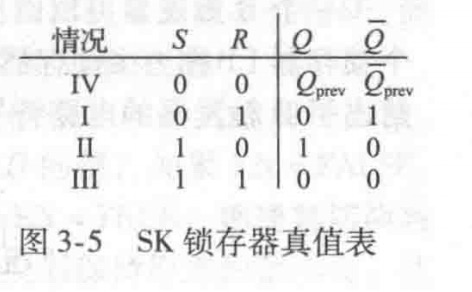

SR锁存器(Set-Reset Latch,SR Latch):由交差耦合的或非门或者与非门组成。Set:给Q置1,Reset:给Q置0。或非门的情况·SR不能同时为0;与非门的情况,SR不能同时为1具体分析。总之Q和!Q必须要相反,因为R和S同时有效的时候是没有意义的,因为锁存器不可能同时被置位和复位。

SR触发器通常是在SR锁存器基础上加了时钟控制信号开关,只在时钟信号的边沿(上升沿或下降沿)到来时才能稳定工作。

状态转移方程:Q = S + R'Q

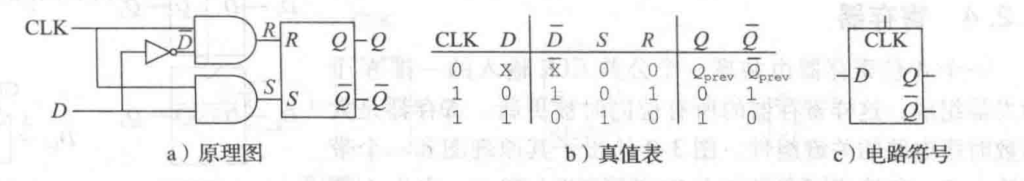

D锁存器(Delay Latch):它有两个输入,数据输入D和时钟输入CLK。当CLK为1时,D锁存器是透明的,就相当于一个缓冲器,输入Q和输入D一致。当CLK为0时,D锁存器是不透明的,Q保持原来的状态不变。

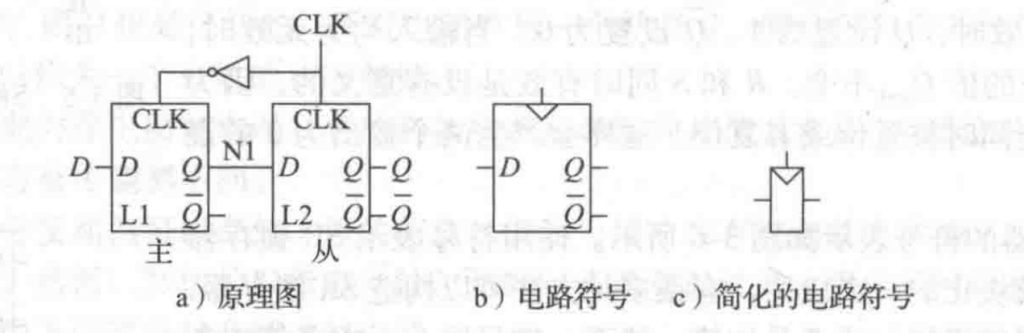

D触发器(Delay Flip-flop,DFF)

结构如图,D触发器是由两个D锁存器串起来的。CLK = 0时,主DFF透明,从DFF不透明,因此N1的传播被切断;CLK = 1时,主DFF不透明,也被切断。只有0到1上升的时期,D的值被复制到Q。一句话概括就是:D触发器在上升沿(rising edge)将D复制到Q,其他时间DFF保持原来的状态。

转移方程是:Q* = Q(⬆️上升沿触发)电路符号里面的倒三角形表示上升沿触发有效,倒三角后面加气泡🫧意为下降沿触发

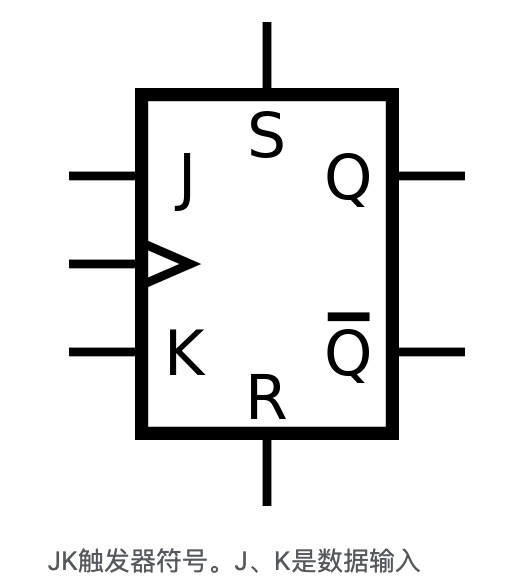

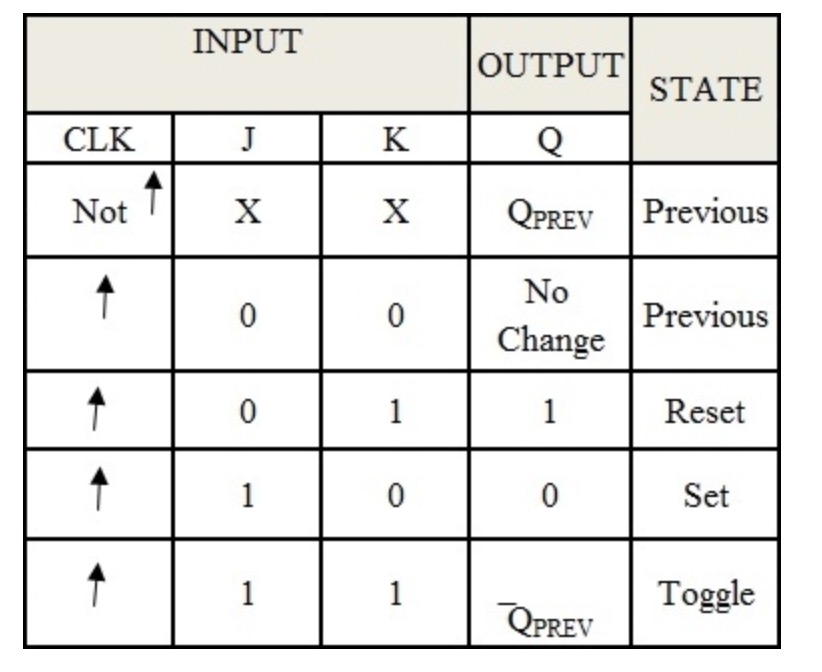

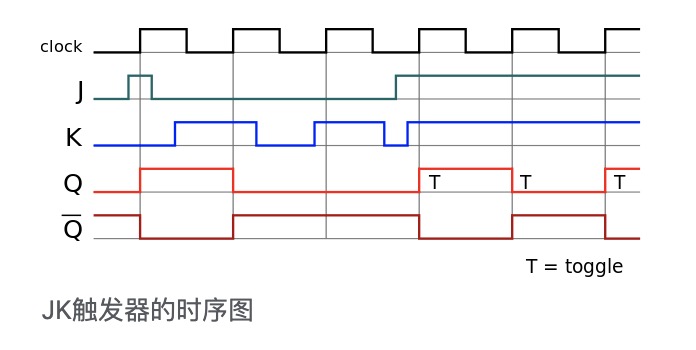

JK触发器

口诀:00不变,11翻转,01、01同J。

JK触发器和触发器中最基本的RS触发器结构相似,其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。当J与K同时变为1的同时,输出的值状态会反转。

锁存器和触发器的关键区别在于工作方式不同,锁存器是在高低电平输入下进行工作,而触发器只在时钟信号的边沿触发时进行工作。

同步时序电路(Synchronous sequential logic):所有寄存器都接受同一个时钟信号(牵一发而动全身❗️)

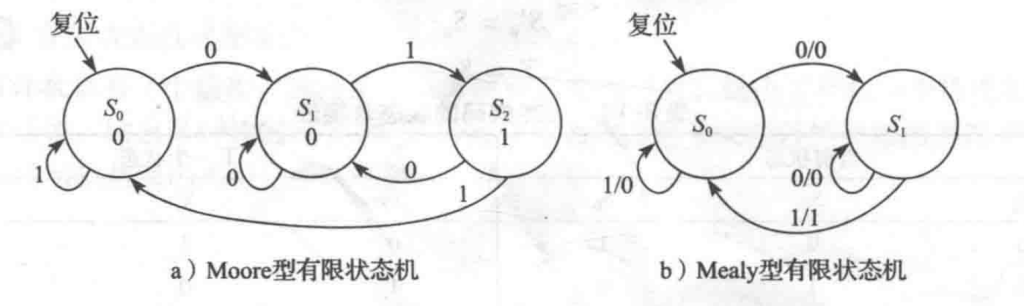

同步时序电路可以用有限状态机(Finite State Machine, FSM)来描述,FSM通常分为2类:

1️⃣Moore型有限状态机:输出仅仅取决于机器当前的状态。(摩尔庄园--摩尔当前)

2️⃣Mealy型有限状态机:输出取决于当前状态和当前输入。每一个弧标记为A/Y。A是引起转换的输入,Y是相应的输出。

同步时序电路的设计题目一般都有很多规律可循!多熟悉!

做题的一般步骤:

1️⃣原始状态图

2️⃣状态化简(等效状态,相同两个状态)

3️⃣状态分配(画状态表的时候与卡诺图一一对应比较合理高效!例如00、01、11、10这样子)

4️⃣选触发器(D、JK;3个状态选2个FF,5个状态选3个FFF)

5️⃣确定激励方程组以及输出方程组

6️⃣画图✍️检查能否自启动

异步时序电路(Asynchronous sequential logic):其中元件(如触发器或逻辑门)的状态变化不受统一的时钟信号控制,而是由元件的输入信号决定。由于设计十分困难,故不做详细笔记。发现了一篇比较好的文章:https://zhuanlan.zhihu.com/p/571811963

补充:状态化简参考文章

完结撒花🎉剩下内容做过去问查漏补缺😇