## Problem 4

Answer the following questions on computer architecture.

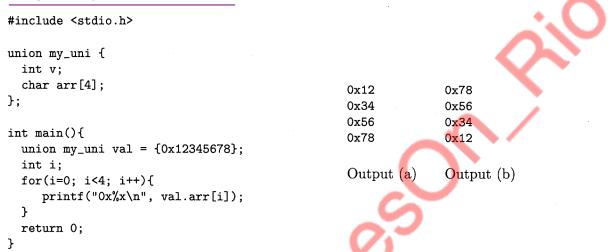

(1) When the following program in C language was compiled and executed on a processor A, the output (a) was obtained. When the same program was compiled and executed on a processor B, the output (b) was obtained. Explain the reason why the difference occurred from the viewpoint of processor architecture.

- (2) Explain data-hazard and control-hazard on a pipeline processor with no forwarding mechanism, using a concrete example.

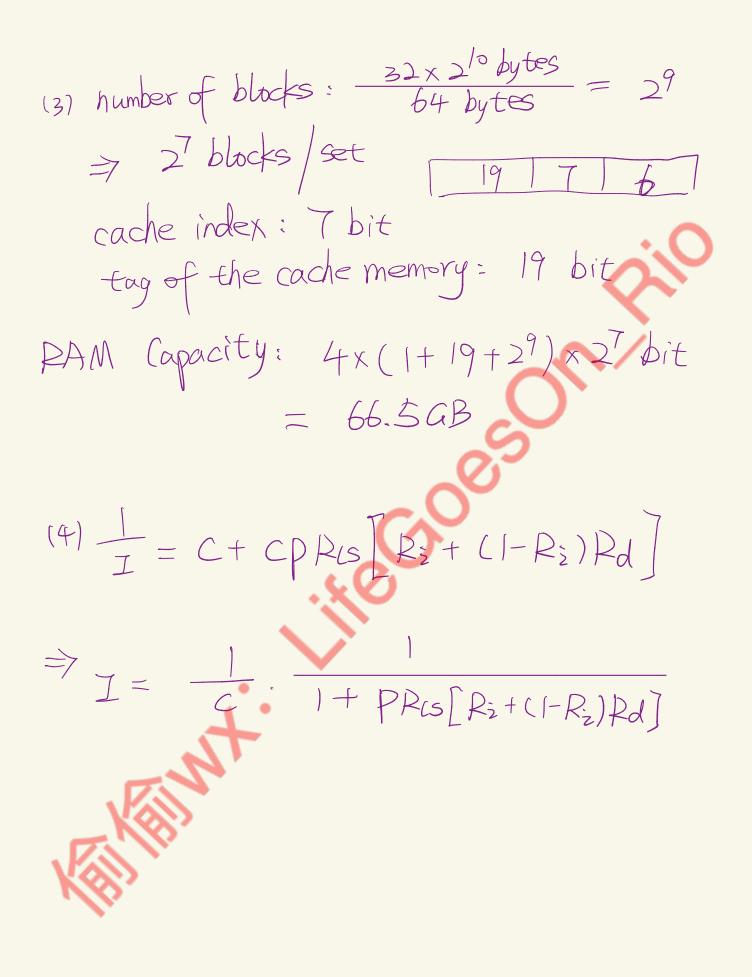

- (3) Consider a 4-way set-associative cache memory that stores totally 32 kibibytes (32 × 2<sup>10</sup> bytes) of data. The address width of the cache memory is 32 bits, and the cache line size (block size) is 64 bytes. Calculate the bit width of the cache index and that of a tag of the cache memory, respectively. Calculate also the total RAM capacity (the number of bits) for storing the tags of the cache memory.

- (4) Consider a processor with an instruction cache and a data cache. Suppose that the CPI (cycles per instruction) of the processor is C when there is no cache miss on both the instruction and data caches. When there is a cache miss on any of the caches, a cache miss penalty of P clock cycles is additionally imposed. Suppose that when a program was executed on the processor, the ratio of the number of load/store instructions to the total number of executed instructions was  $R_{ls}$ . Suppose also that, for that program execution, the cache miss rate of the instruction cache was  $R_i$ , the cache miss rate of the data cache was  $R_d$ , and the IPC (instructions per cycle) of the processor was I. Express I in terms of C,  $R_i$ ,  $R_d$ ,  $R_{ls}$ , and P.

12) Pdata hazard happens when the result of the current instruction is not ready but the following instruction needs. 9: add \$3,\$1,\$2 SW \$3,0(\$4)

② control hazard happens when the instructions can't be executed until the branch condition is confirmed.

eg: beg \$1,\$2, Else Else: Sub \$3,\$4,\$5